- 您现在的位置:买卖IC网 > Sheet目录362799 > EVAL-AD1837AEB (Analog Devices, Inc.) 2 ADC, 8 DAC, 96 kHz, 24-Bit Codec

REV. B

AD1837

–13–

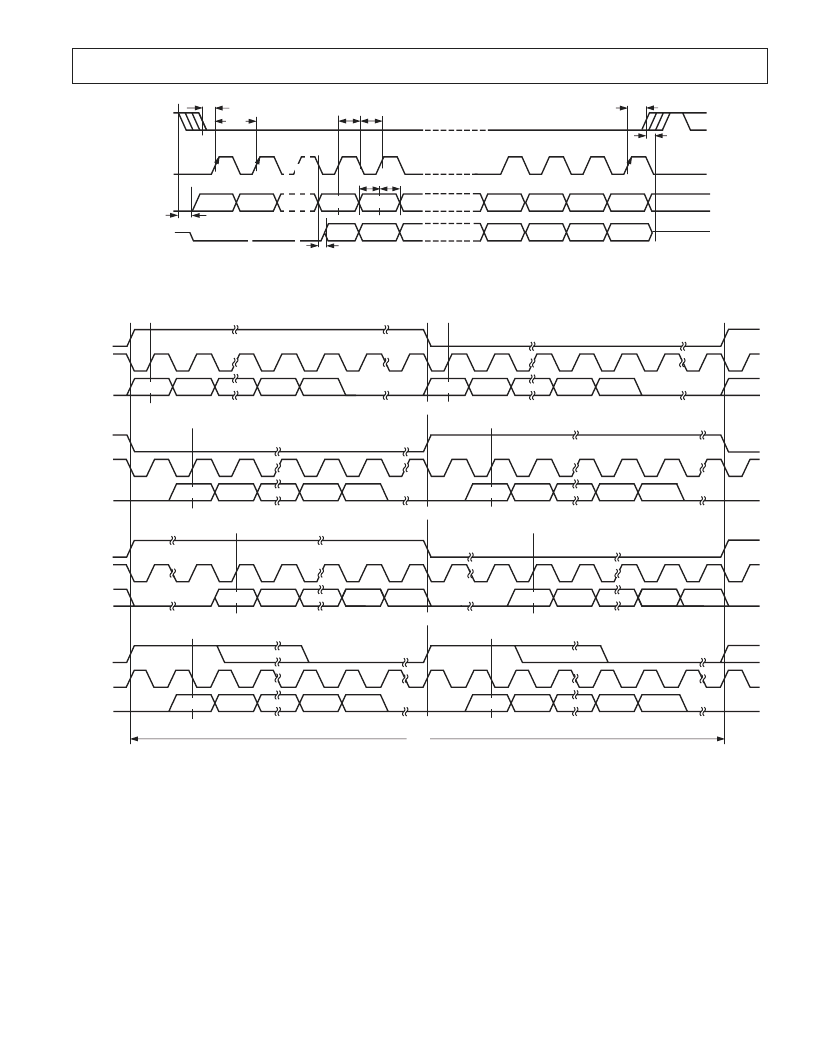

CLATCH

CCLK

CIN

COUT

D0

D8

D0

D15

D14

D9

D8

t

CCH

t

CCL

D9

t

CDS

t

CDH

t

CLS

t

CLH

t

COD

t

COTS

t

CCP

t

COE

Figure 3. Format of SPI Timing

LRCLK

BCLK

SDATA

LRCLK

BCLK

SDATA

LRCLK

BCLK

SDATA

LRCLK

BCLK

SDATA

LEFT CHANNEL

RIGHT CHANNEL

LEFT CHANNEL

RIGHT CHANNEL

LEFT CHANNEL

RIGHT CHANNEL

MSB

MSB

MSB

MSB

MSB

MSB

MSB

MSB

LSB

LSB

LSB

LSB

LSB

LSB

LSB

LSB

LEFT-JUSTIFIED MODE—16 BITS TO 24 BITS PER CHANNEL

I

2

S MODE—16 BITS TO 24 BITS PER CHANNEL

RIGHT-JUSTIFIED MODE—SELECT NUMBER OF BITS PER CHANNEL

DSP MODE—16 BITS TO 24 BITS PER CHANNEL

1/

f

S

NOTES

1. DSP MODE DOES NOT IDENTIFY CHANNEL.

2. LRCLK NORMALLY OPERATES AT

f

EXCEPT FOR DSP MODE WHICH IS 2

f

S.

3. BCLK FREQUENCY IS NORMALLY 64 LRCLK BUT MAY BE OPERATED IN BURST MODE.

Figure 4. Stereo Serial Modes

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

EVAL-AD1838AEB

2 ADC, 6 DAC, 96KHZ 24 BIT CODEC

EVAL-AD1852EB

24-Bit Stereo DAC Evaluation Board

EVAL-AD1870EB

Single-Supply 16-Bit Stereo ADC

EVAL-AD1896EB

Automotive Low-Cost Non-Volatile FPGA Family; Voltage: 1.2V; Grade: -5; Package: Lead-Free ftBGA; Pins: 256; Temperature: AUTO; LUTs (k): 8

EVAL-AD1928EBZ

2 ADC/8 DAC with PLL, 192 kHz, 24-Bit Codec

EVAL-AD1928EB

2 ADC/8 DAC with PLL, 192 kHz, 24-Bit Codec

EVAL-AD1938EB

4 ADC/8 DAC with PLL, 192 kHz, 24 Bit CODEC

EVAL-AD1939EB

4 ADC/8 DAC with PLL, 192 kHz, 24 Bit CODEC

相关代理商/技术参数

EVAL-AD1837EB

制造商:Analog Devices 功能描述:EVALUATION BOARD I.C. - Bulk

EVAL-AD1838AEB

制造商:Analog Devices 功能描述:EVALUATION BOARD I.C. - Bulk

EVAL-AD1838EB

制造商:Analog Devices 功能描述:Evaluation Board For 2 ADC, 8DAC 96 KHz, 24-Bit Sigma Delta Codec 制造商:Analog Devices 功能描述:EVALUATION BOARD I.C. - Bulk

EVAL-AD1839AEB

制造商:Analog Devices 功能描述:EVALUATION BOARD I.C. - Bulk

EVAL-AD1839EB

制造商:Analog Devices 功能描述:EVALUATION BOARD I.C. - Bulk

EVAL-AD1852EB

制造商:Analog Devices 功能描述:Evaluation Kit For 24Bit Stereo DAC Evaluation Board 制造商:Analog Devices 功能描述:STEREO,192KHZ VLTG OUTPUT SGMA DELTA DAC - Bulk

EVAL-AD1852EBZ

制造商:AD 制造商全称:Analog Devices 功能描述:Stereo, 24-Bit, 192 kHz, Multibit, Sigma-Delta DAC

EVAL-AD1853EB

制造商:Analog Devices 功能描述:EVALBRD 192KHZ MULTIBIT SIGMA DELTA DAC - Bulk